Tema 2

Arquitectura de la familia AVR

Sistemas embebidos

Contenidos

Introducción.

Diagrama de bloques.

Mapa de memoria.

Interrupciones.

Temporizadores.

Watchdog.

Acceso directo a memoria (DMA).

Periféricos internos.

Introducción

Familia AVR

Microcontroladores de 8 bits, de bajo consumo y alto rendimiento.

Aquitectura RISC avanzada.

135 instrucciones (la mayor parte se ejecutan en un ciclo de reloj).

32 registros de 8 bits de propósito general.

Hasta 16 MIPS a 16MHz @ 4,5V-5,5V.

64/128/256 KBytes de memoria FLASH ISP (10K ciclos escritura/borrado).

4 KBytes de memoria EEPROM (100K ciclos escritura/borrado).

8 KBytes de memoria SRAM.

Microcontrolador AVR

El ATmega2560 es el microcontrolador utilizado en la tarjeta Arduino MEGA 2560 (revisión 3).

Es el microcontrolador más potente de la familia:

Pinout microcontrolador

Pinout microcontrolador

Descripción de las señales del microcontrolador:

- VCC/GND

Alimentación de 5 V

- nRESET

Entrada de reset.

- XTAL1/XTAL2

Entrada/salida del oscilador.

- AVCC/AREF

Alimentación y referencia del convertidor A/D.

- Port A (PA7..PA0)

Puerto A

Pinout microcontrolador

Descripción de las señales del microcontrolador:

- Port B (PB7..PB0)

Puerto B (el de mayor fanout)

- Port C (PC7..PC0)

Puerto C

- Port D (PD7..PD0)

Puerto D

- Port E (PE7..PE0)

Puerto E

- Port F (PF7..PF0)

Puerto F (entradas convertidor A/D e interfaz JTAG)

Pinout microcontrolador

Descripción de las señales del microcontrolador:

- Port G (PG7..PG0)

Puerto G

- Port H (PH7..PH0)

Puerto H

- Port J (PJ7..PJ0)

Puerto J

- Port K (PK7..PK0)

Puerto K (entradas convertidor A/D)

- Port L (PL7..PL0)

Puerto L

Puerto general de E/S

Diagrama de bloques

Diagrama de bloques completo

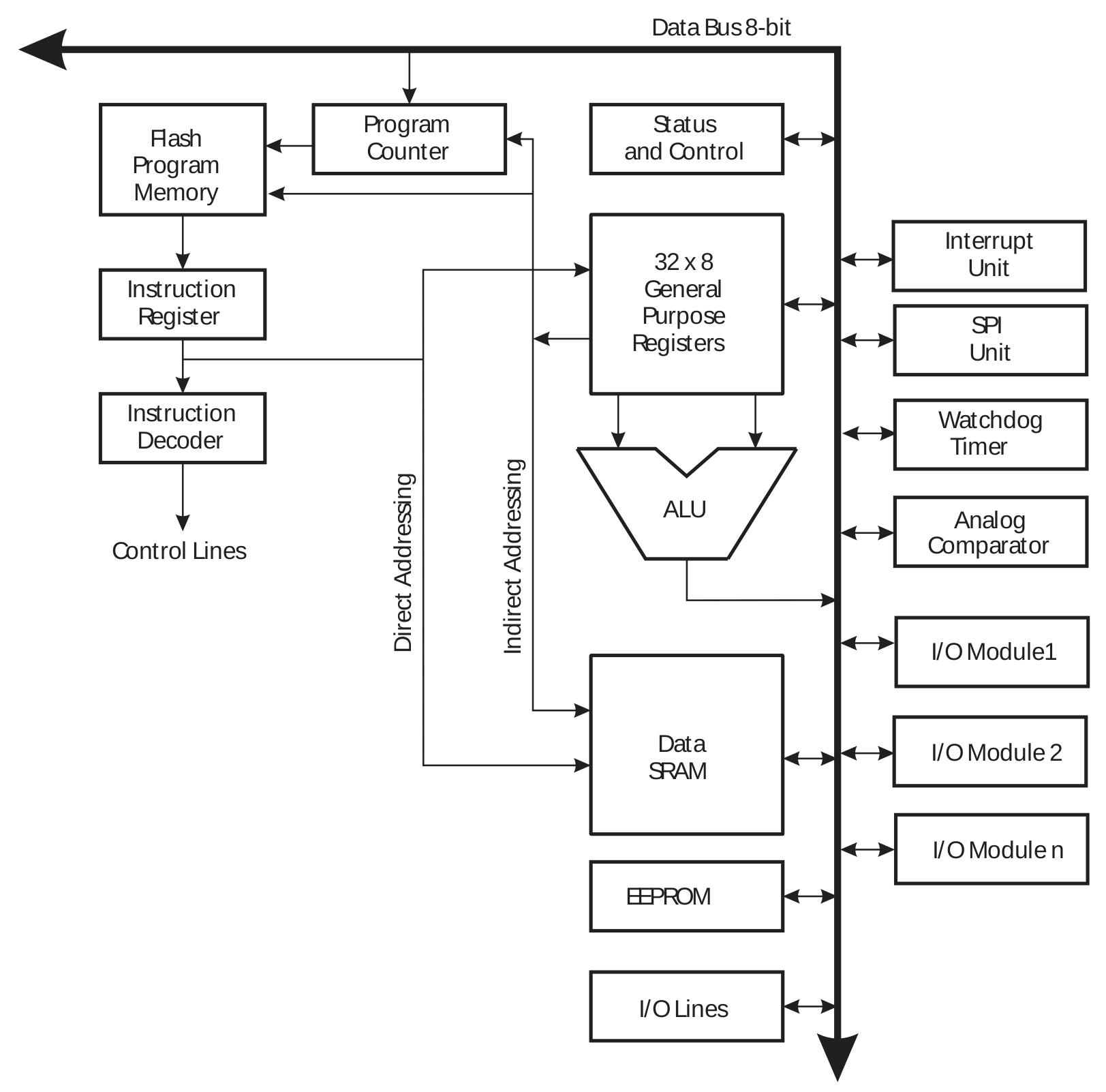

Diagrama de bloques CPU AVR

Arquitectura CPU AVR

Arquitectura Hardvard (memoria y buses separados para el programa y los datos).

Mientras una instrucción se ejecuta, la siguiente se extrae de la memoria de programa.

Esto permite que la mayor parte de las instrucciones se ejecuten en un ciclo de reloj.

Espacios de memoria con direccionamiento lineal.

32 registros de 8 bits de propósito general (R0..R31).

6 registros de 8 bits (R26..R31) pueden utilizarse como 3 registros de 16 bits (X, Y, Z).

Registros de propósito general

Unidad aritmético lógica

Realiza operaciones aritméticas y lógicas en un ciclo de reloj entre:

Registros de propósito general.

Un registro de propósito general y un valor constante.

Tras cada operación, el registro de estado (SREG) se actualiza reflejando la información sobre el resultado.

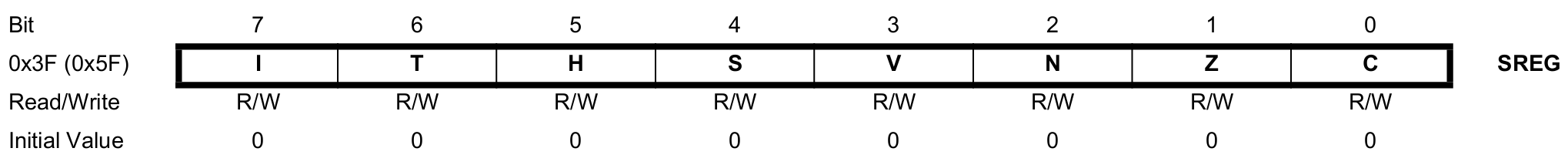

Registro de estado

- Bit 7 - I

Global interrupt Enable

- Bit 6 - T

Bit Copy Storage

- Bit 5 - H

Half Carry Flag

- Bit 4 - S

Sign Bit

Registro de estado

- Bit 3 - V

Two’s Complement Overflow Flag

- Bit 2 - N

Negative Flag

- Bit 1 - Z

Zero Flag

- Bit 0 - C

Carry Flag

Puntero de pila

La pila se utiliza para almacenar:

Datos temporales.

Variables locales.

Direcciones de retorno de interrupciones y subrutinas.

El puntero de pila apunta a la parte superior de la memoria de pila (en la memoria SRAM).

El puntero de pila se decrementa cuando un dato se guarda en la pila (push).

El puntero de pila se incrementa cuando un dato se extrae de la pila (pop).

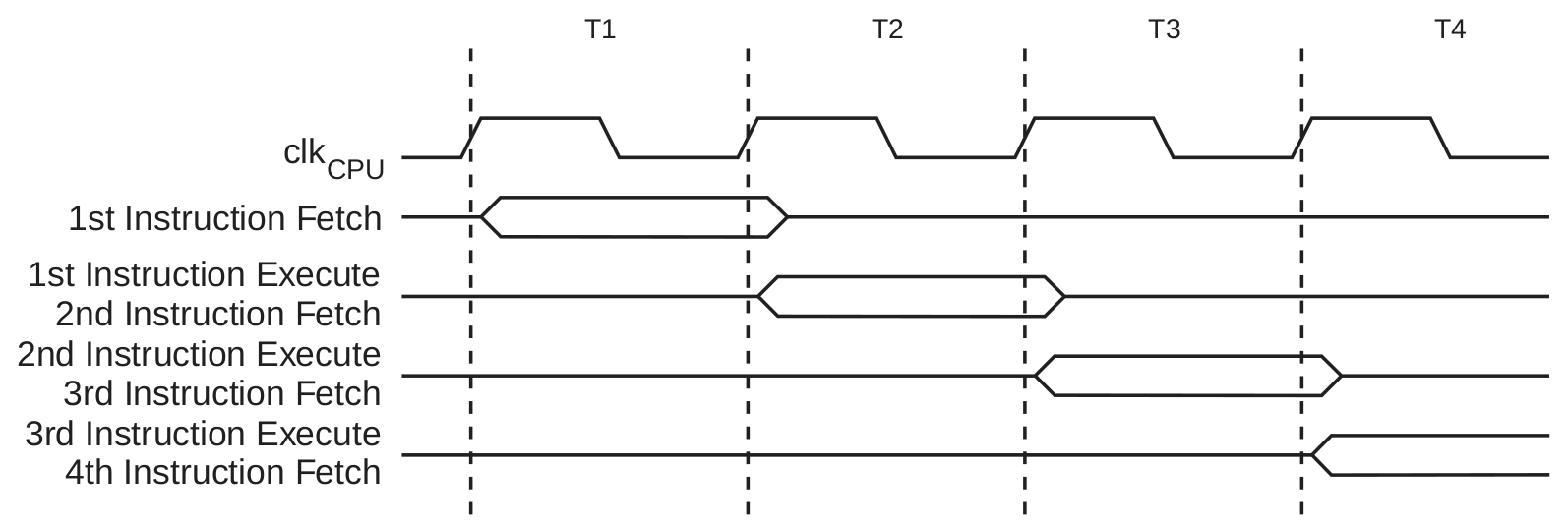

Ejecución de instrucciones

La CPU AVR utiliza directamente la señal de reloj (sin divisores internos).

La ejecución de instrucciones tiene un rendimiento máximo de 1 MIPS por MHz.

Juego de instrucciones

135 instrucciones (la mayor parte se ejecutan en un ciclo de reloj).

Ejemplo parpadeo led

Código fuente en lenguaje C:

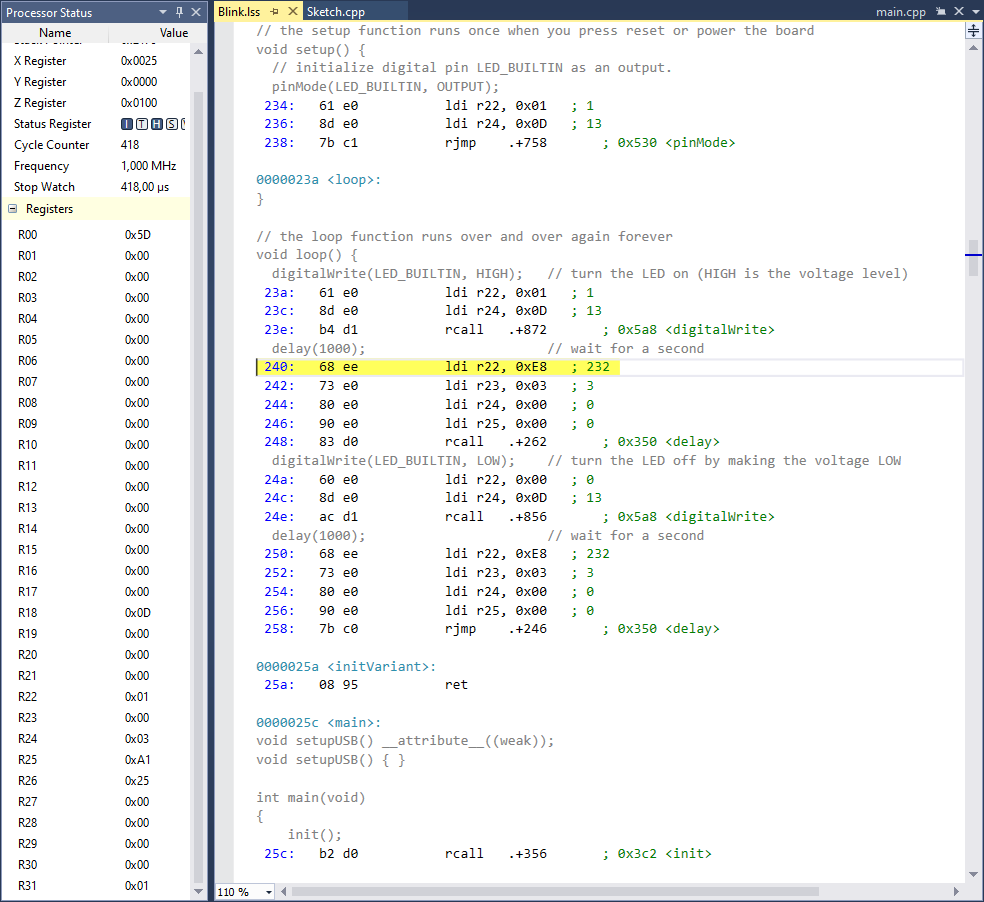

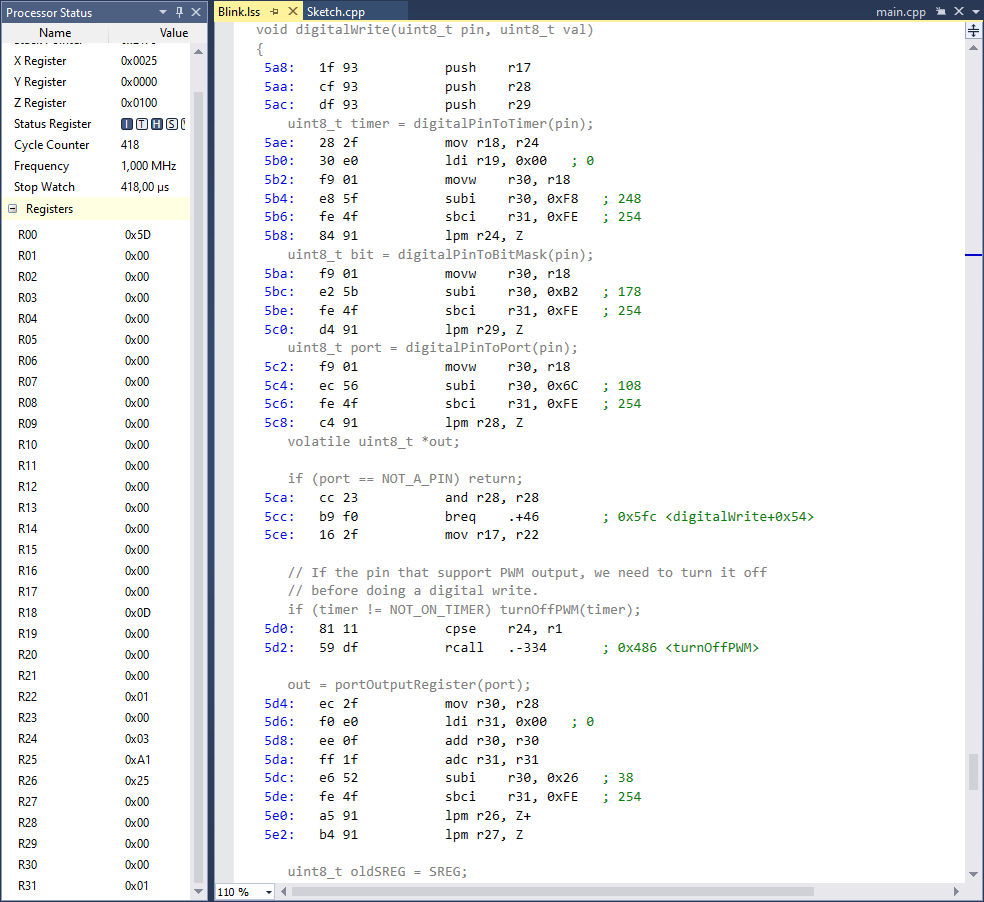

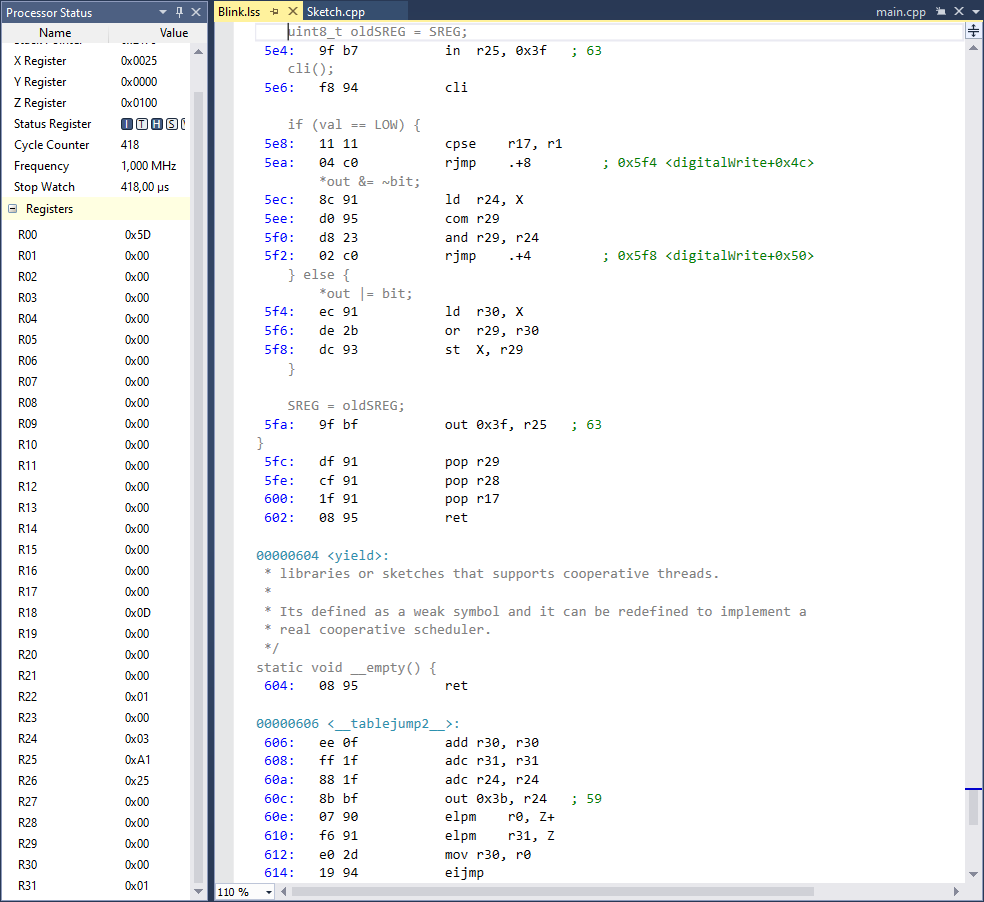

Ejemplo parpadeo led

Código fuente en lenguaje ensamblador:

Ejemplo parpadeo led

Código fuente en lenguaje ensamblador:

Ejemplo parpadeo led

Código fuente en lenguaje ensamblador:

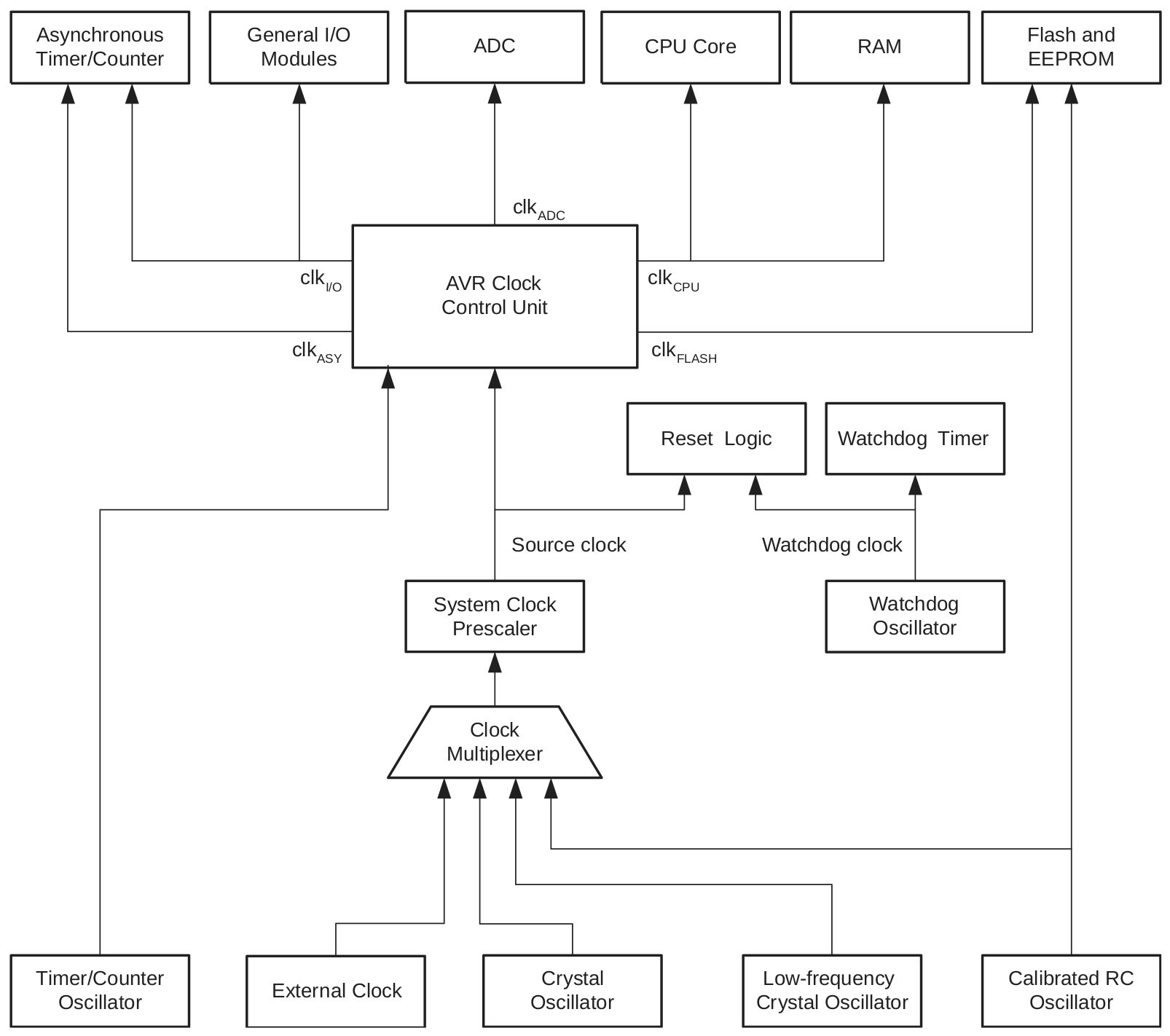

Distribución del reloj

Reset

Mapa de memoria

Mapa de memoria

Utiliza tres espacios de memoria independientes:

Memoria de programa en FLASH.

Memoria de datos en SRAM.

Memoria de almacenamiento de datos permanente en EEPROM.

Los tres espacios de memoria utilizan direccionamiento lineal.

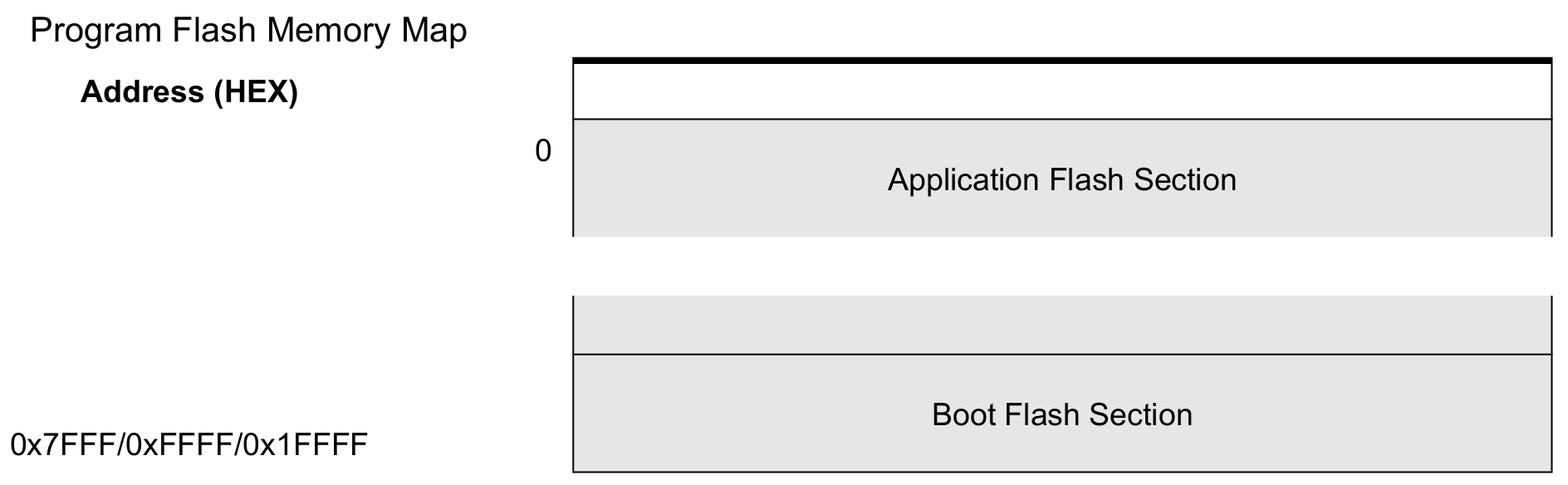

Memoria de program FLASH

Se divide en dos secciones: arranque y aplicación.

La memoria está organizada en 128K palabras de 16 bits.

El contador de programa (PC) tiene 17 bits.

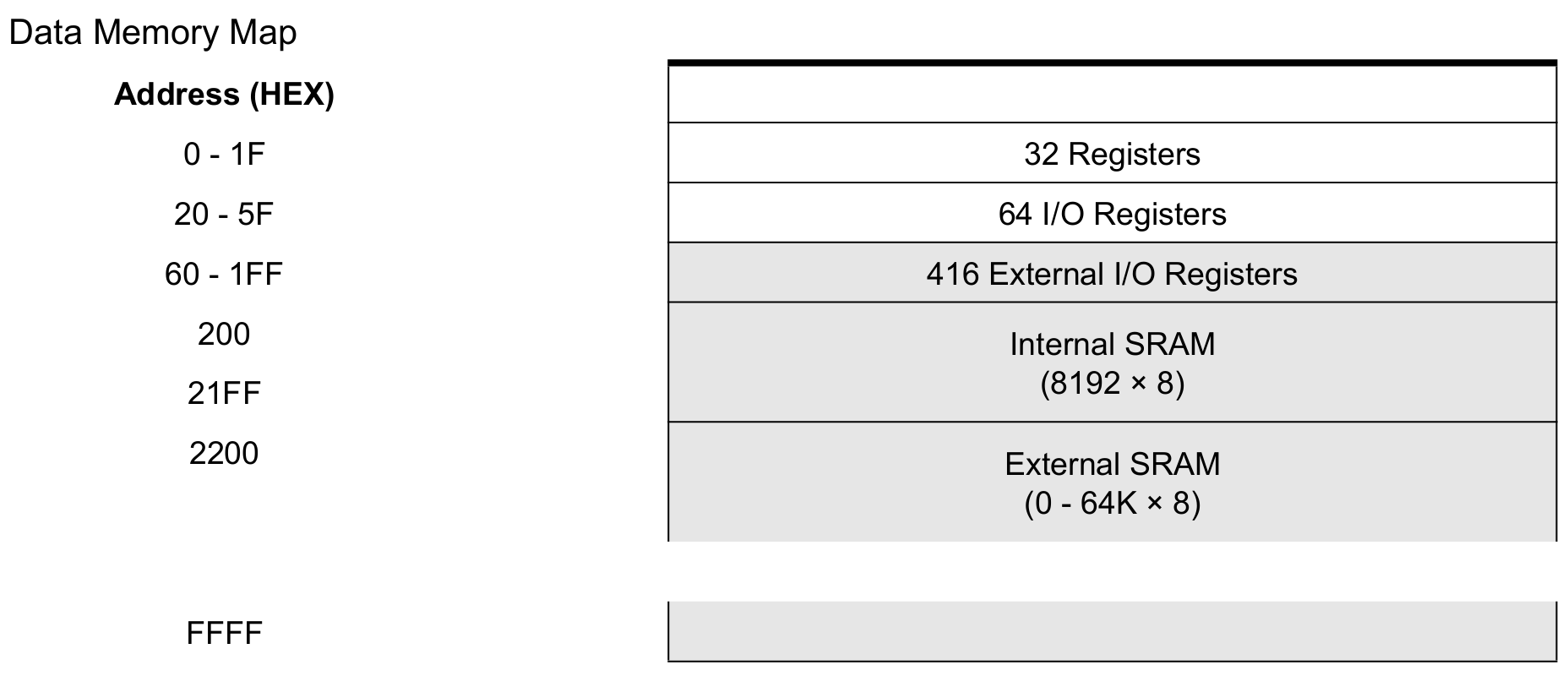

Memoria de datos SRAM

Los 8 KBytes de memoria de datos interna se pueden ampliar con una memoria externa de hasta 64 KBytes.

Interrupciones

Interrupciones

La CPU AVR dispone de varias fuentes de interrupción.

Cada fuente de interrupción utiliza su propio vector de interrupción.

Cuando se produce una interrupción, la ejecución del programa se redirige a la rutina de atención de la interrupción a la que apunta su vector de interrupción.

Cuando finaliza la rutina de atención a la interrupción, se reanuda la ejecución del programa.

Adicionalmente al bit global de habilitación de interrupciones del registro de estado, cada interrupción tiene asociado un bit independiente de habilitación.

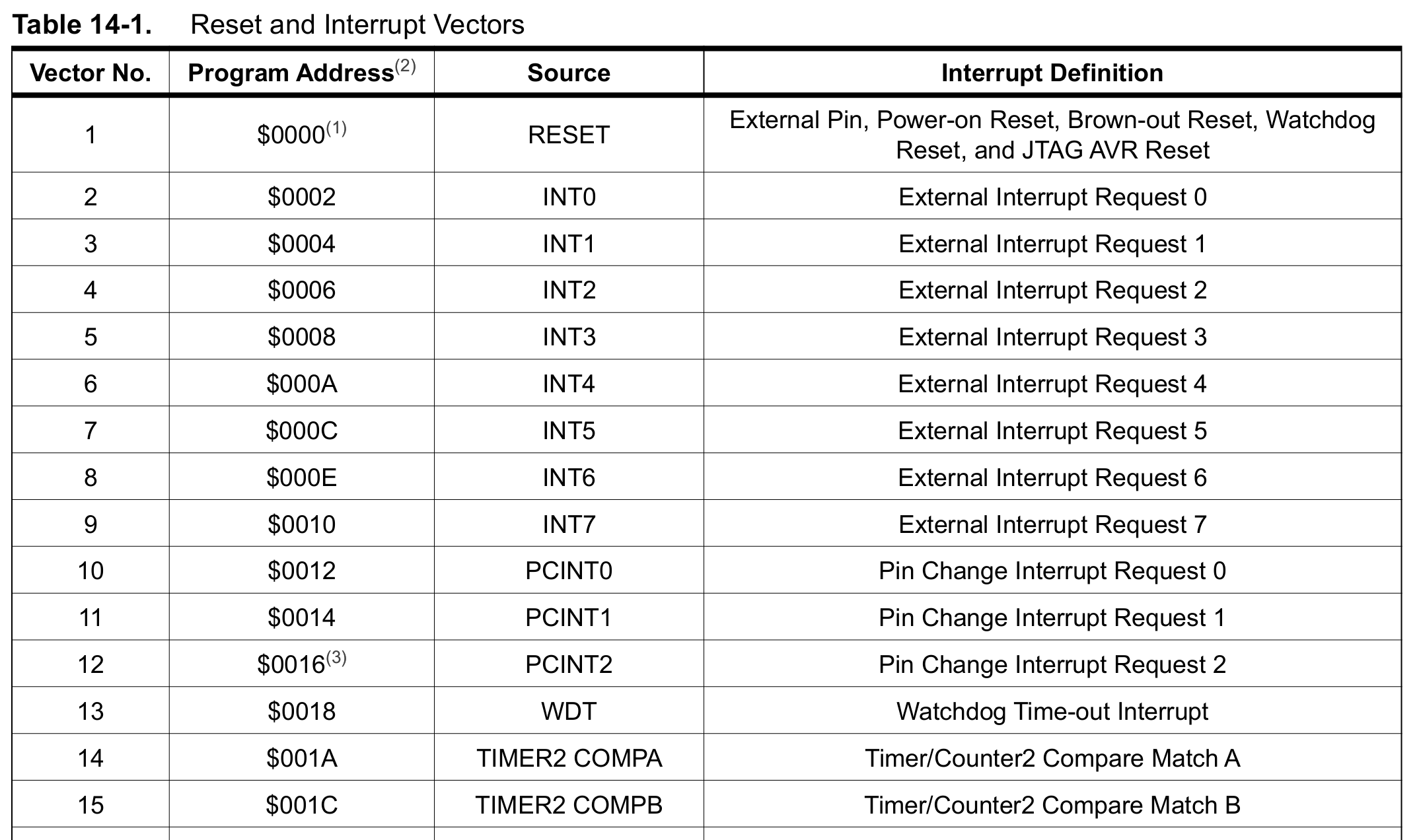

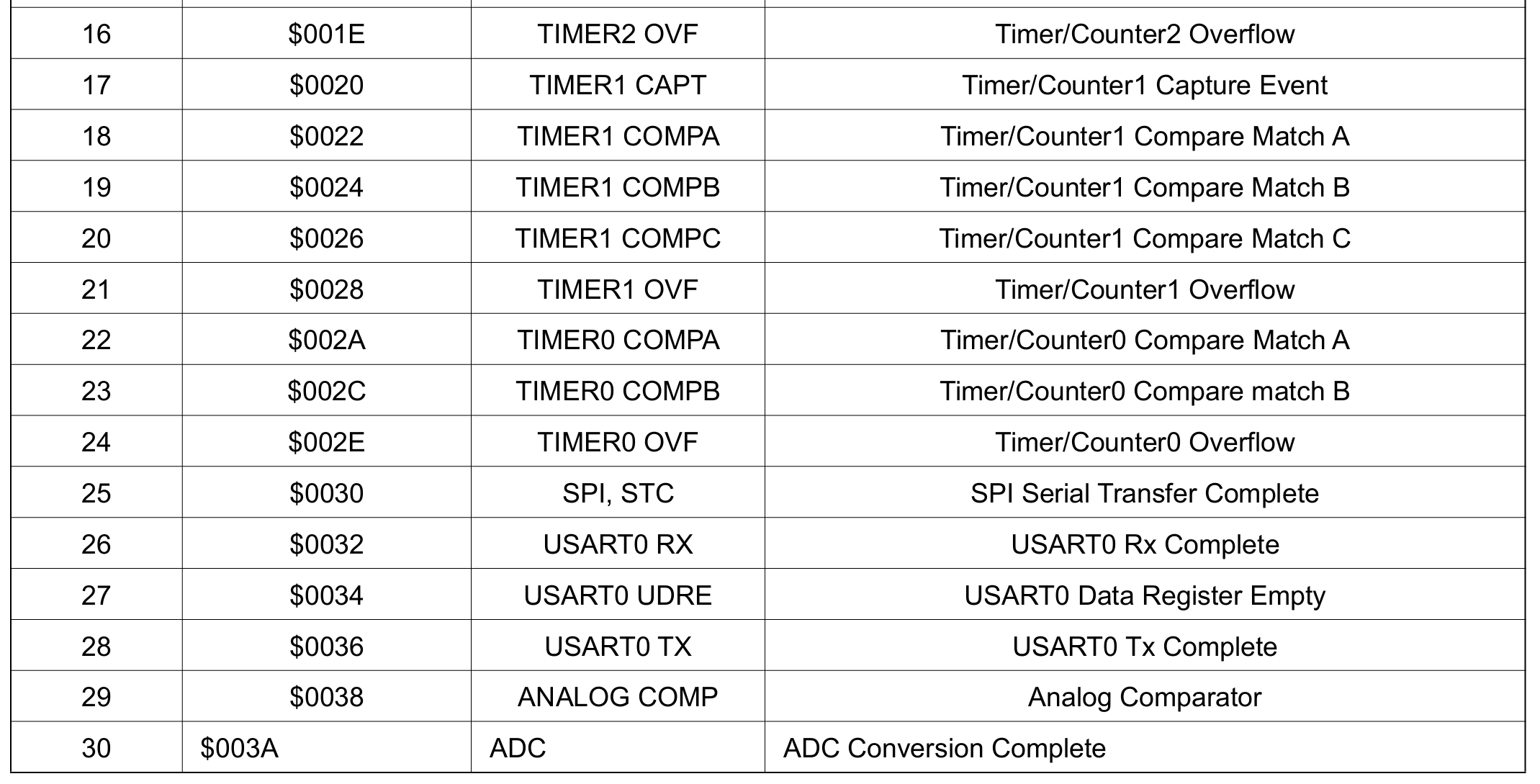

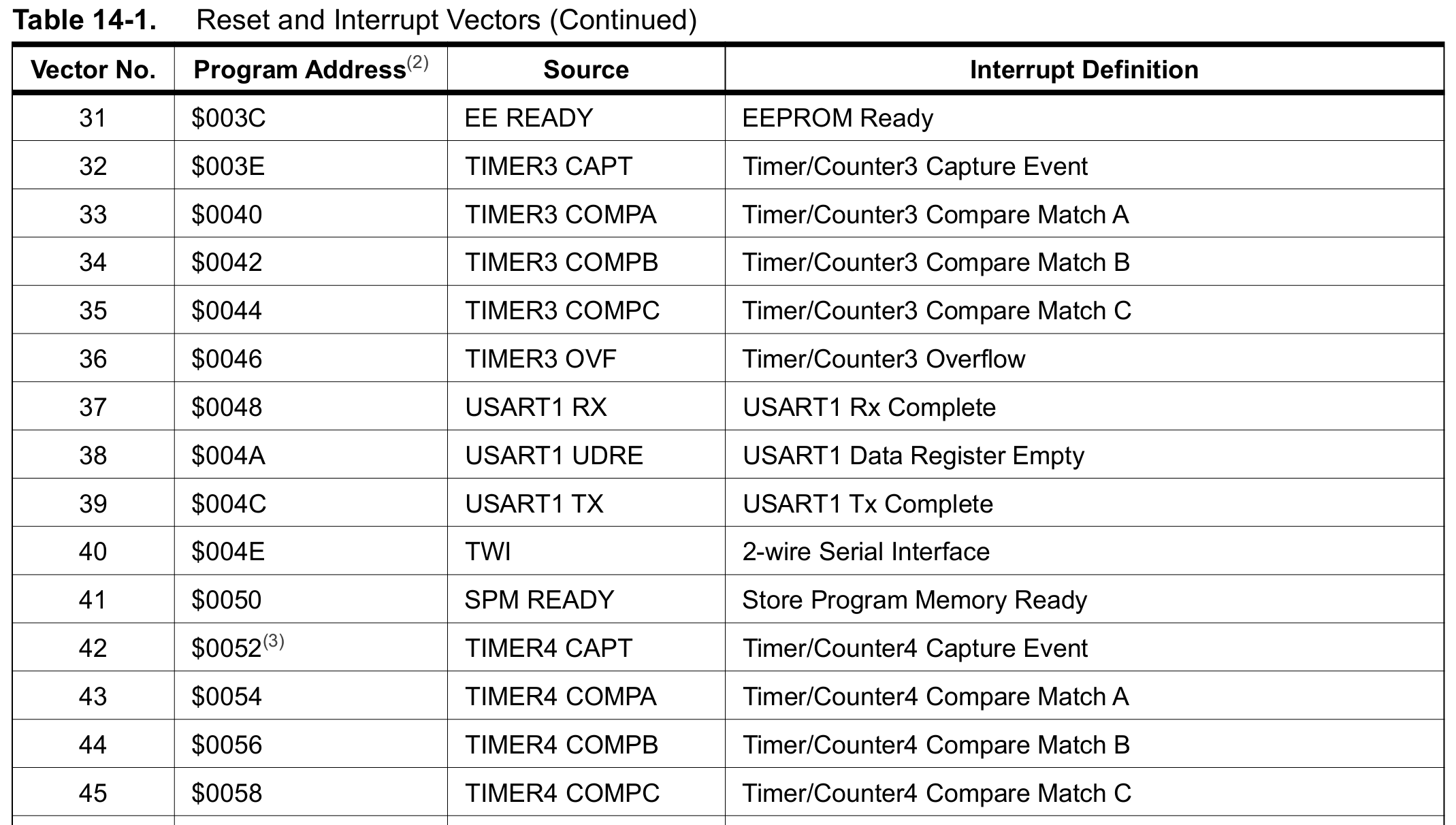

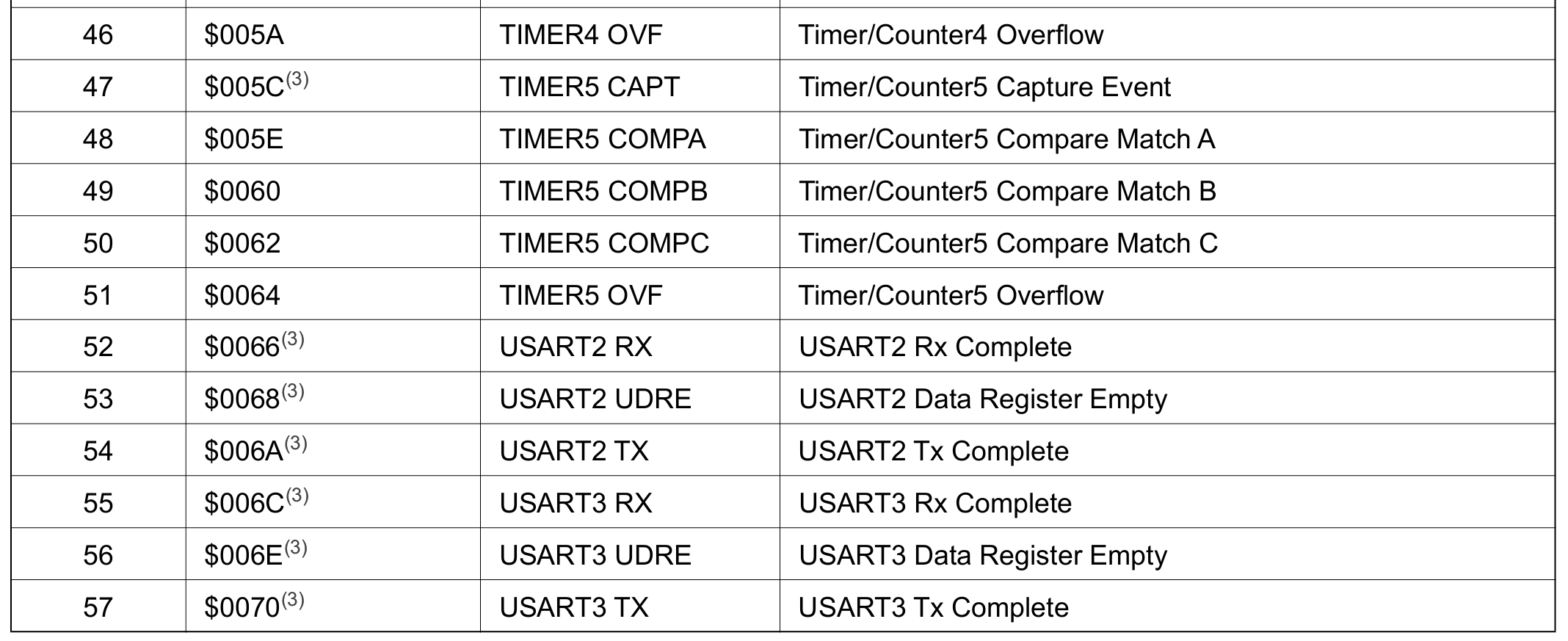

Vectores de interrupción

Vectores de interrupción

Vectores de interrupción

Vectores de interrupción

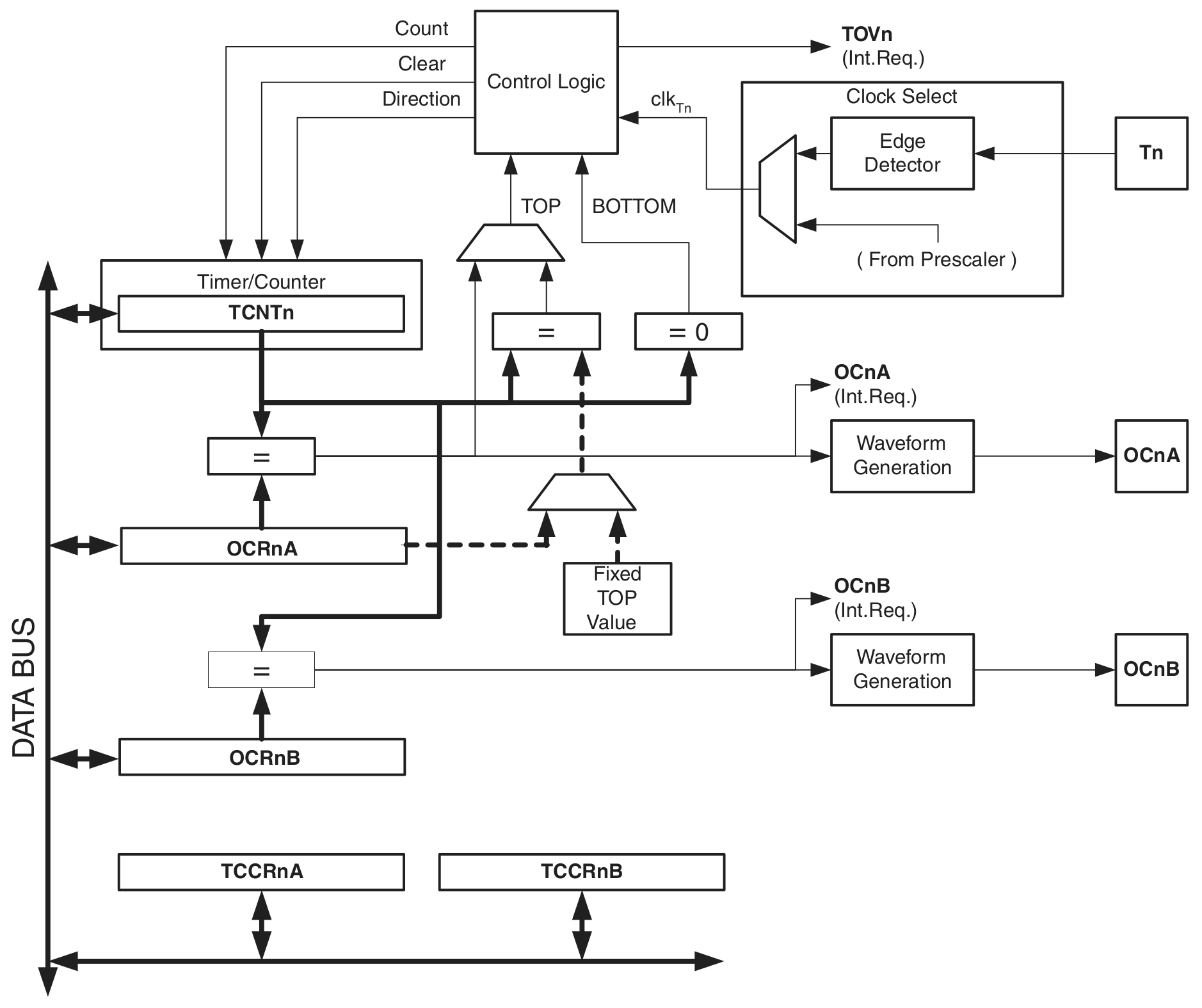

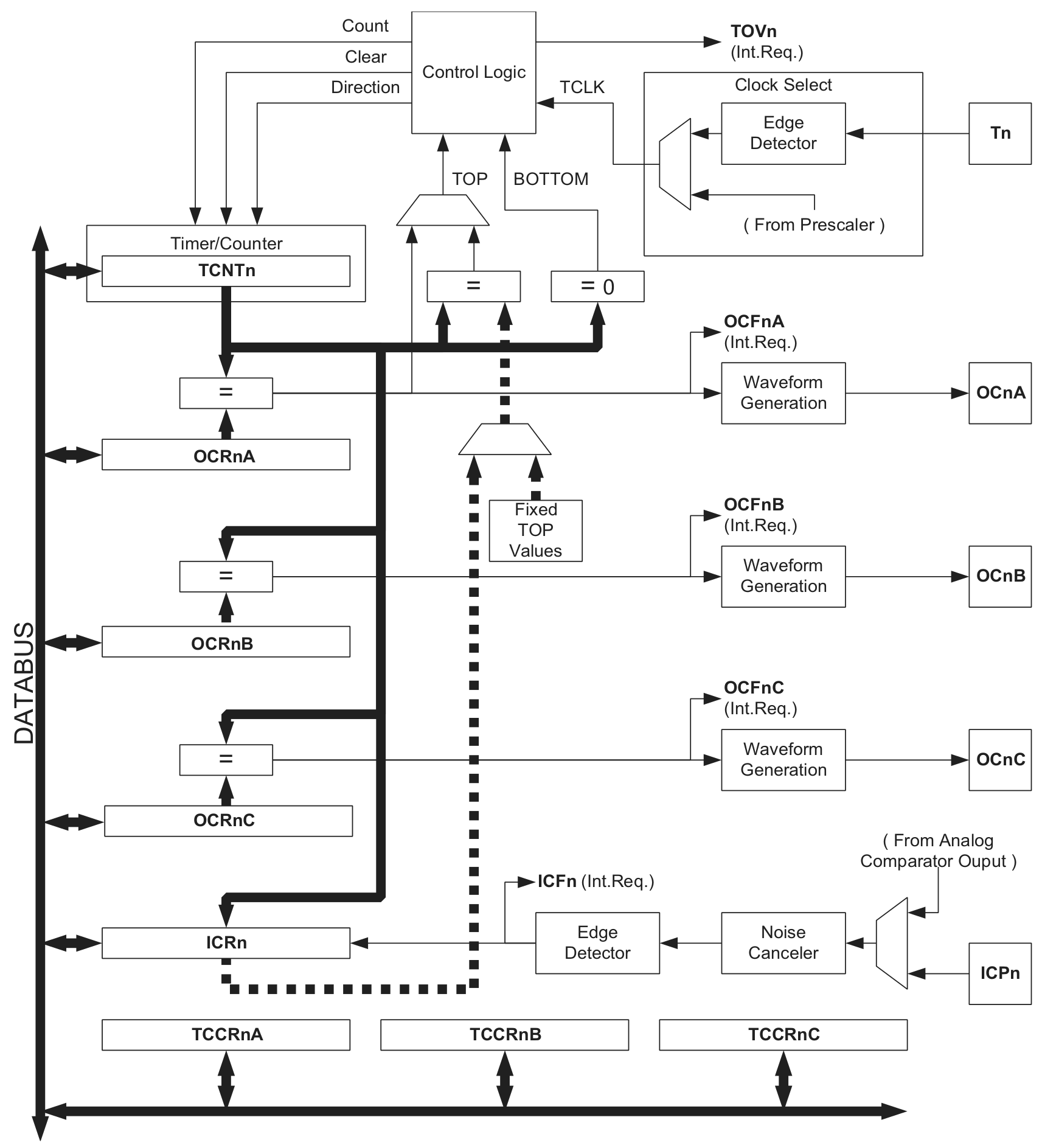

Temporizadores

Temporizadores

2 temporizadores/contadores de 8 bits (T0 y T2).

4 canales PWM de 8 bits (canales A y B).

4 temporizadores/contadores de 16 bits (T1, T3, T4 y T5).

12 canales PWM de 16 bits (canales A, B y C).

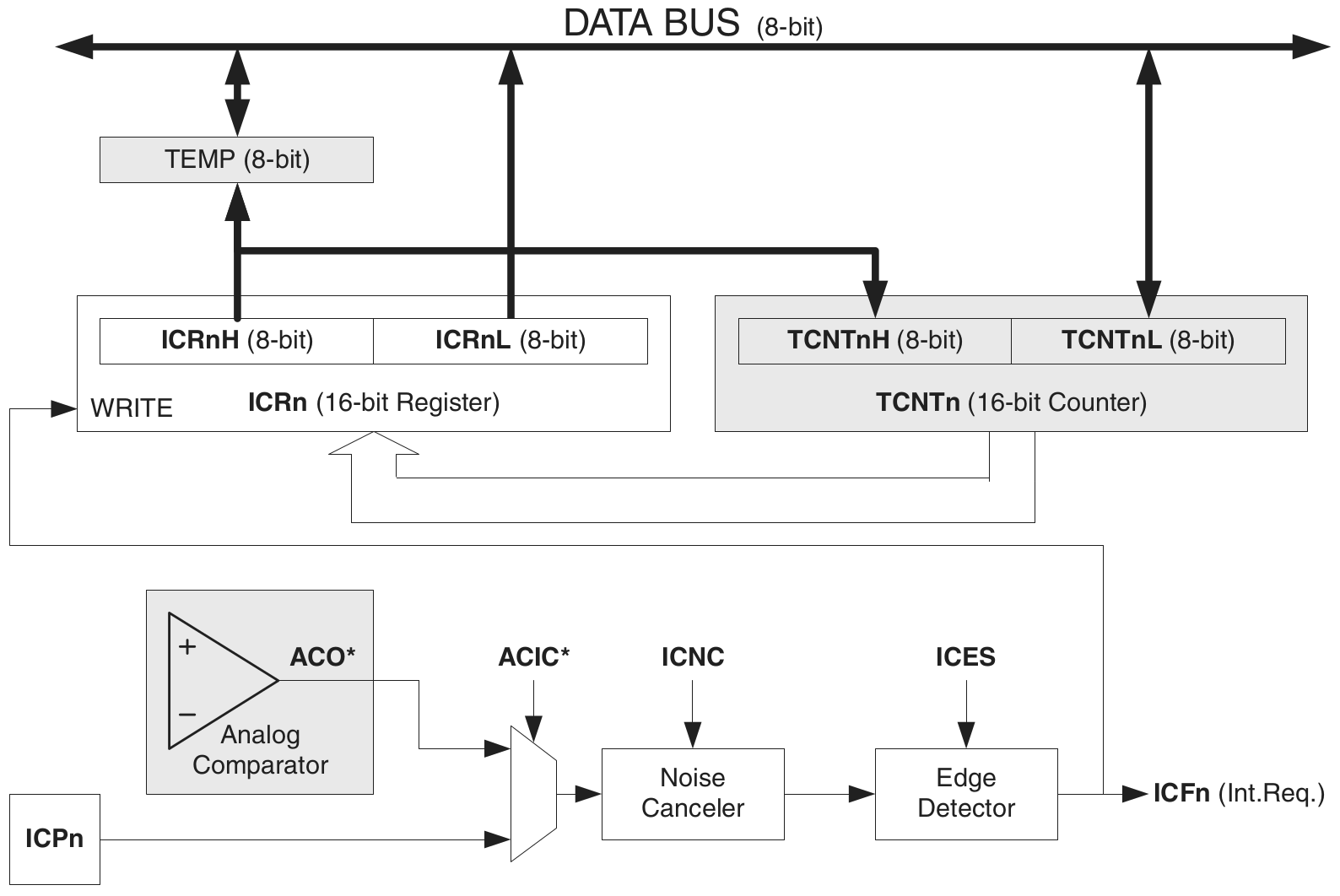

1 canal de captura de entrada digital/analógica.

Temporizadores de 8 bits

Temporizadores de 16 bits

Salida PWM

Captura de entrada

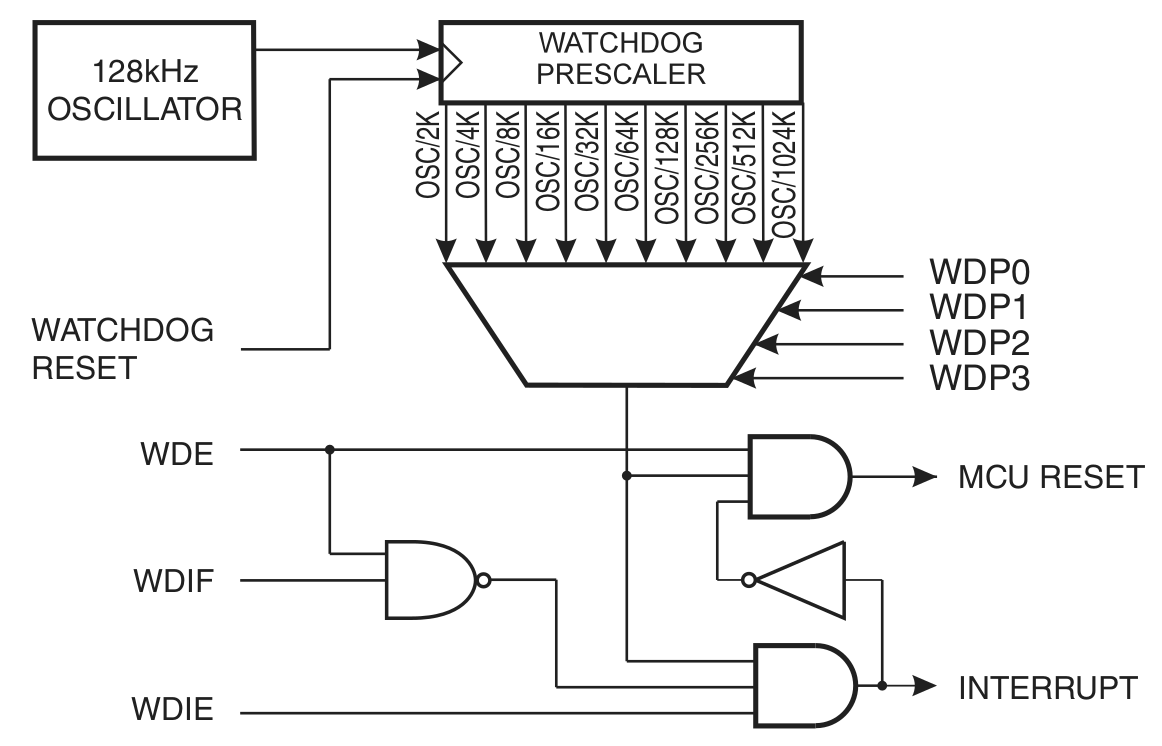

Watchdog

Watchdog

Utiliza una fuente de reloj independiente (oscilador interno de 128 kHz).

Tres modos de operación:

Interrupción.

Reset del sistema.

Interrupción y reset del sistema.

Timeout configurable entre 16 ms y 8 s.

Si la aplicación no reinicia el temporizador del watchdog antes de que venza el timeout, se generará un reset del sistema (o una interrupción).

Temporizador del watchdog

Reset del watchdog

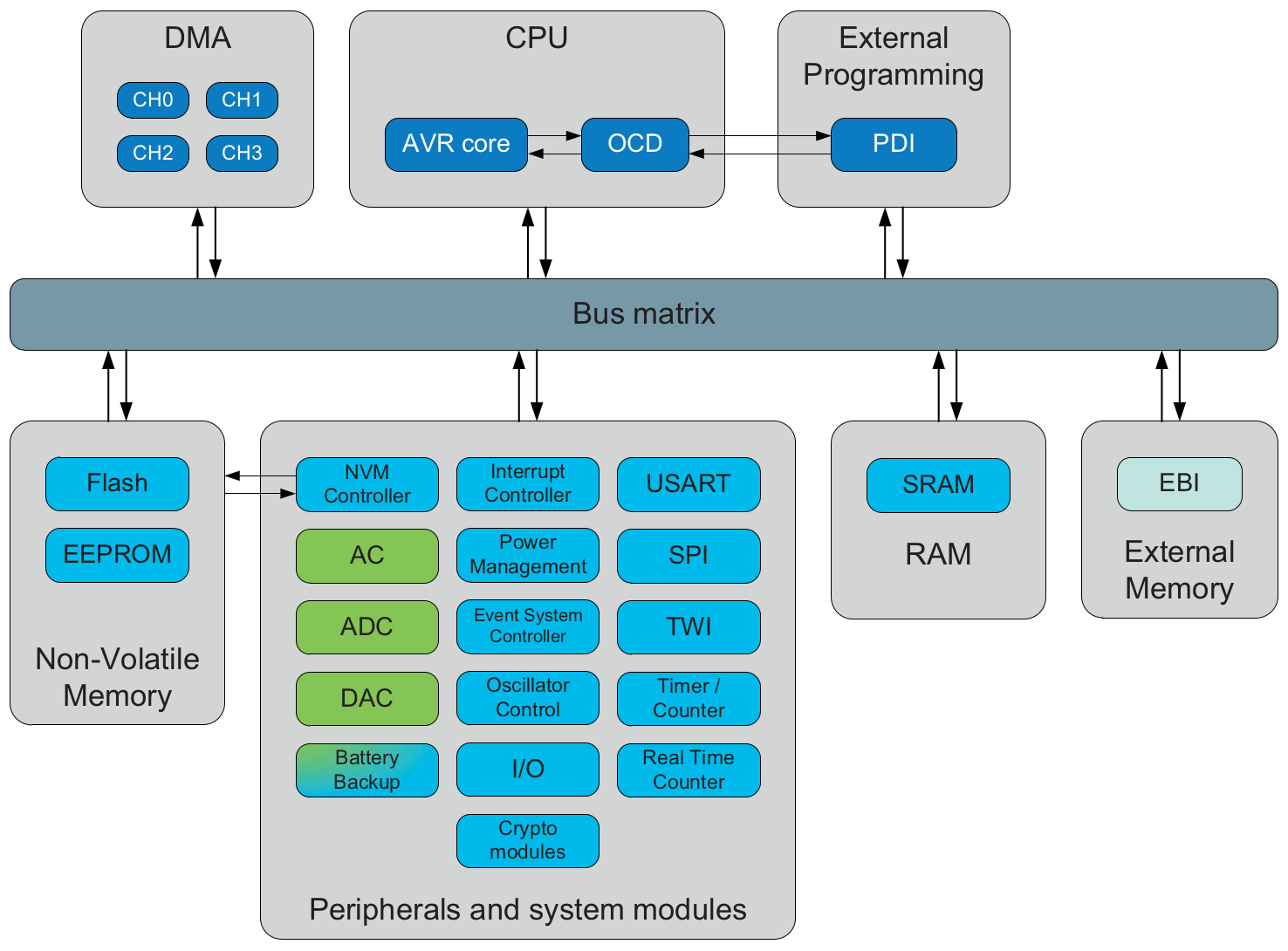

Acceso directo a memoria (DMA)

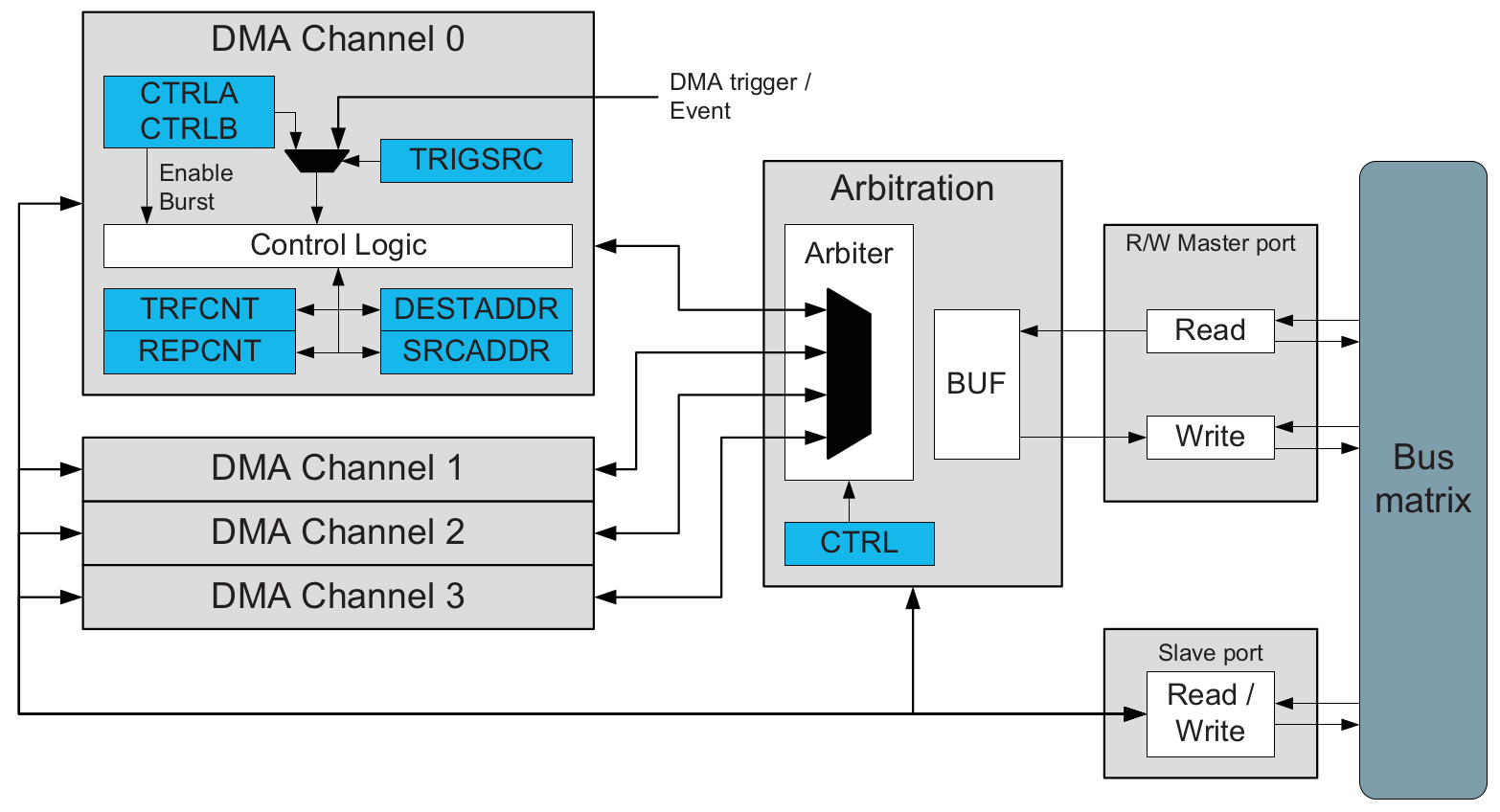

Acceso directo a memoria (DMA)

Un controlador DMA permite realizar transferencias de datos entre memorias y periféricos sin intervención de la CPU.

La familia AVR ATmega no incorpora ningún controlador DMA.

La familia AVR ATxmega sí incorpora un controlador DMA.

El microcontrolador ATxmega256 incorpora un controlador DMA de 4 canales.

Cada canal puede transferir bloques configurables de 1 byte a 64 Kbytes.

Las direcciones de la fuente y el destino pueden configurarse independientemente en autoincremento, autodecremento o estático.

Acceso directo a memoria (DMA)

Acceso directo a memoria (DMA)

Periféricos internos

Periféricos internos

Convertidor A/D de 16 canales.

Convertidor D/A (no disponible en ATmega).

Comunicaciones cableadas:

Cuatro USART.

Un bus serie I2C.

Un bus serie SPI.

Convertidor A/D

Convertidor de aproximaciones sucesivas (SAR) con 10 bits de resolución.

16 canales multiplexados (single ended).

14 canales diferenciales (7+7 canales y 1+1 negativos).

4 canales diferenciales con ganancia ajustable x10 y x200.

Referencia de tensión interna de 1,1V y 2,56V o externa.

Velocidad de conversión de hasta 76,9 kSPS (15 kSPS a la máxima resolución).

Convertidor A/D

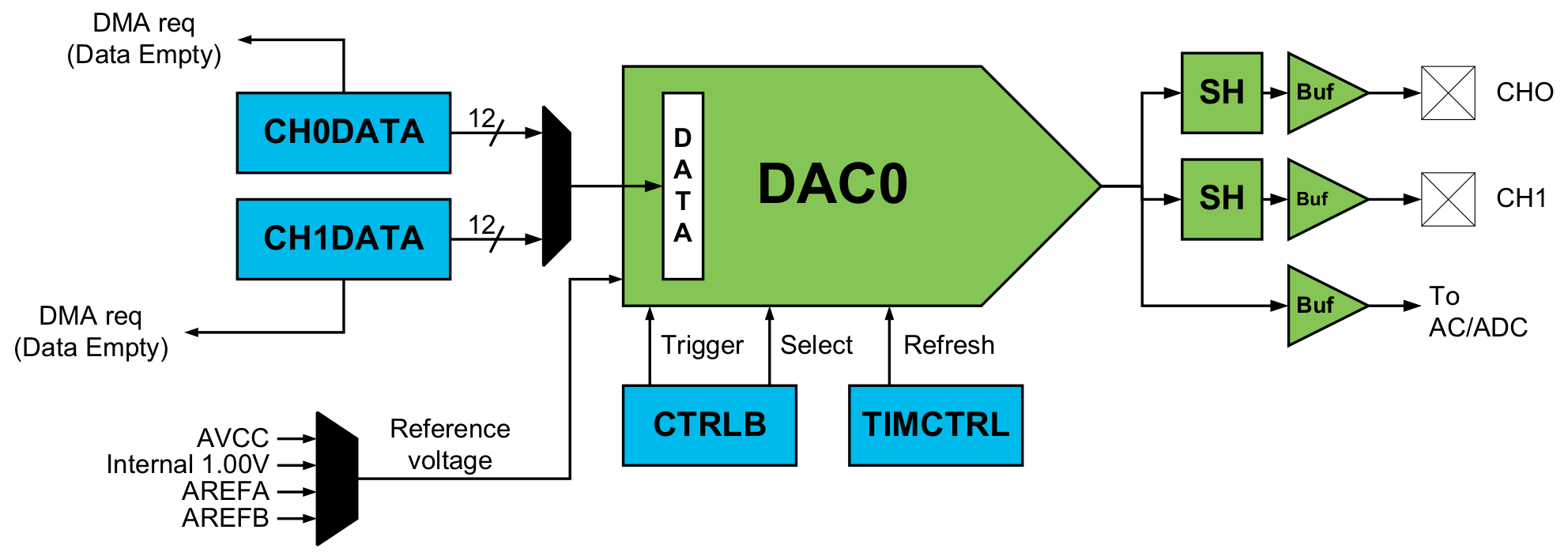

Convertidor D/A (ATxmega)

Convertidor de 12 bits de resolución.

2 canales independientes.

Referencia de tensión interna de 1,00V o externa.

Velocidad de conversión de hasta 1 MSPS.

Convertidor D/A (ATxmega)